1.Про інтегральні схеми

1.1 Поняття та народження інтегральних схем

Інтегральна схема (IC): відноситься до пристрою, який поєднує в собі активні пристрої, такі як транзистори та діоди, з пасивними компонентами, такими як резистори та конденсатори, за допомогою ряду спеціальних методів обробки.

Схема або система, яка «інтегрована» на пластину напівпровідника (наприклад, кремнію або сполук, таких як арсенід галію) відповідно до певних взаємозв’язків схем, а потім упакована в оболонку для виконання певних функцій.

У 1958 році Джек Кілбі, який відповідав за мініатюризацію електронного обладнання в Texas Instruments (TI), запропонував ідею інтегральних схем:

«Оскільки всі компоненти, такі як конденсатори, резистори, транзистори тощо, можна виготовити з одного матеріалу, я подумав, що можна зробити їх на шматку напівпровідникового матеріалу, а потім з’єднати між собою, щоб утворити повну схему».

12 та 19 вересня 1958 року Кілбі завершив виробництво та демонстрацію генератора фазового зсуву та тригера, відповідно, ознаменувавши народження інтегральної схеми.

У 2000 році Кілбі був удостоєний Нобелівської премії з фізики. Нобелівський комітет якось прокоментував, що Кілбі «заклав основу для сучасних інформаційних технологій».

На малюнку нижче показано Кілбі та його патент на інтегральну схему:

1.2 Розвиток технології виготовлення напівпровідників

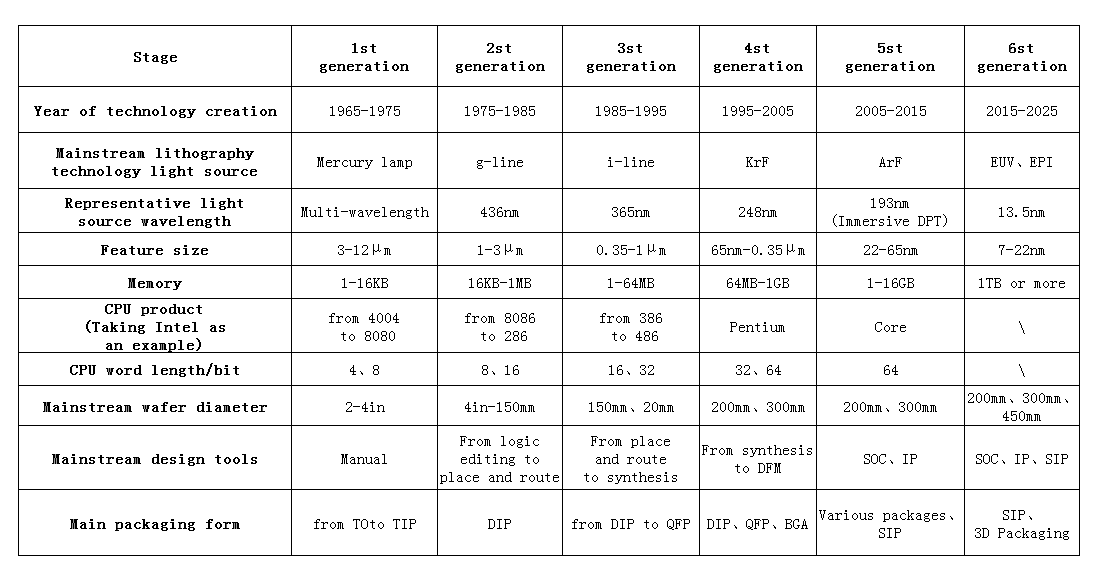

На наступному малюнку показано етапи розвитку технології виготовлення напівпровідників:

1.3 Промислова мережа інтегральних схем

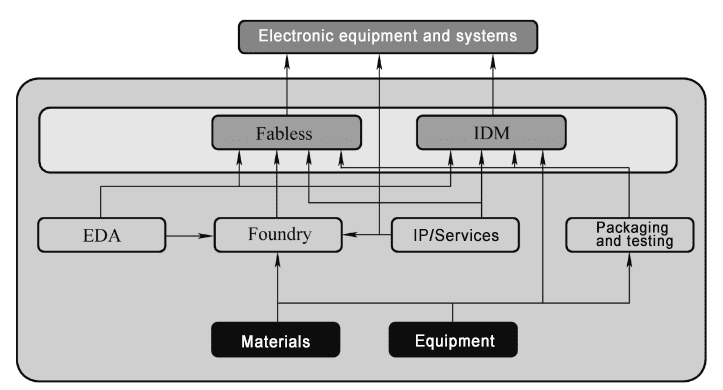

Склад ланцюжка напівпровідникової промисловості (переважно інтегральних схем, включаючи дискретні пристрої) показаний на малюнку вище:

- Fabless: компанія, яка розробляє продукти без виробничої лінії.

- IDM: Integrated Device Manufacturer, виробник інтегрованих пристроїв;

- IP: Виробник схемного модуля;

- EDA: Electronic Design Automatic, автоматизація електронного проектування, компанія в основному надає засоби проектування;

- Ливарний цех; Ливарне виробництво пластин, що надає послуги з виробництва мікросхем;

- Ливарні компанії з пакування та тестування: в основному обслуговують Fabless та IDM;

- Компанії з виробництва матеріалів і спеціального обладнання: в основному забезпечують необхідні матеріали та обладнання для компаній-виробників мікросхем.

Основною продукцією, що виробляється з використанням напівпровідникової технології, є інтегральні схеми та дискретні напівпровідникові пристрої.

Основні продукти інтегральних схем включають:

- Специфічні стандартні частини (ASSP);

- мікропроцесорний блок (МПУ);

- Пам'ять

- Спеціальна інтегральна схема (ASIC);

- Аналогова схема;

- Загальна логічна схема (Logical Circuit).

Основна продукція напівпровідникових дискретних приладів включає:

- діод;

- транзистор;

- Силовий пристрій;

- Високовольтний пристрій;

- мікрохвильовий прилад;

- Оптоелектроніка;

- Сенсорний пристрій (Sensor).

2. Процес виробництва інтегральних схем

2.1 Виробництво мікросхем

На кремнієвій пластині можна виготовляти десятки або навіть десятки тисяч конкретних мікросхем одночасно. Кількість мікросхем на кремнієвій пластині залежить від типу продукту та розміру кожної мікросхеми.

Кремнієві пластини зазвичай називають підкладками. Діаметр кремнієвих пластин з роками збільшувався від менш ніж 1 дюйма на початку до загальновживаних 12 дюймів (приблизно 300 мм) зараз і переходить до 14 або 15 дюймів.

Виробництво мікросхем зазвичай поділяється на п’ять етапів: підготовка кремнієвої пластини, виготовлення кремнієвої пластини, випробування/вибір мікросхеми, складання та пакування та остаточне тестування.

(1)

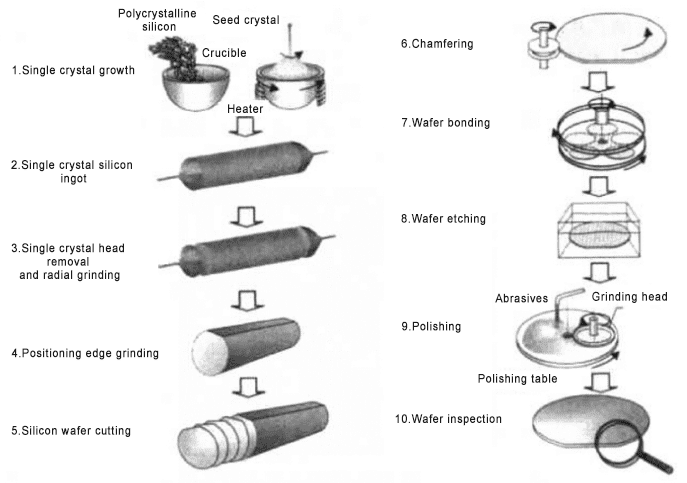

Підготовка кремнієвих пластин:

Для виготовлення сировини кремній добувають із піску та очищають. Спеціальний процес виробляє кремнієві злитки відповідного діаметру. Потім злитки розрізають на тонкі кремнієві пластини для виготовлення мікросхем.

Вафлі готуються відповідно до певних специфікацій, таких як вимоги до реєстраційних країв і рівні забруднення.

(2)Виробництво кремнієвих пластин:

Також відомий як виробництво мікросхем, чиста кремнієва пластина надходить на завод з виробництва кремнієвих пластин, а потім проходить різні етапи очищення, формування плівки, фотолітографії, травлення та легування. Оброблена кремнієва пластина має повний набір інтегральних схем, постійно вигравіруваних на кремнієвій пластині.

(3)Випробування та вибір кремнієвих пластин:

Після завершення виробництва кремнієвих пластин кремнієві пластини відправляються в зону випробування/сортування, де окремі мікросхеми досліджуються та електрично випробовуються. Прийнятні та неприйнятні чіпи потім сортуються, а браковані чіпи маркуються.

(4)Збірка та упаковка:

Після тестування/сортування пластини переходять на етап складання та пакування для упаковки окремих чіпів у захисну трубку. Тильна сторона пластини шліфована для зменшення товщини підкладки.

Товста пластикова плівка прикріплюється до тильної сторони кожної пластини, а потім лезо пилки з алмазним наконечником використовується для відокремлення чіпсів на кожній пластині вздовж ліній різця на лицьовій стороні.

Пластикова плівка на зворотному боці силіконової пластини запобігає падінню кремнієвого чіпа. На складальному заводі хороші чіпи пресуються або вакуумуються для формування складального пакету. Пізніше чіп запечатується в пластикову або керамічну оболонку.

(5)Підсумковий тест:

Щоб забезпечити функціональність мікросхеми, кожну упаковану інтегральну схему перевіряють на відповідність вимогам виробника до параметрів електричних і екологічних характеристик. Після остаточного тестування чіп відправляється замовнику для складання в спеціально відведене місце.

2.2 Поділ процесу

Процеси виробництва інтегральних схем зазвичай поділяються на:

Інтерфейс: Вхідний процес зазвичай відноситься до процесу виробництва таких пристроїв, як транзистори, в основному включаючи процеси формування ізоляції, структури затвора, витоку та стоку, контактних отворів тощо.

Бекенд: Внутрішній процес в основному стосується формування з’єднувальних ліній, які можуть передавати електричні сигнали до різних пристроїв на мікросхемі, в основному включаючи такі процеси, як осадження діелектрика між з’єднувальними лініями, утворення металевих ліній і формування свинцевих прокладок.

Середня стадія: Щоб покращити продуктивність транзисторів, передові технологічні вузли після 45 нм/28 нм використовують затворні діелектрики з високим ступенем k і металеві затворні процеси, а також додають замінні затворні процеси та процеси локального з’єднання після підготовки структури витоку та стоку транзистора. Ці процеси знаходяться між зовнішнім процесом і внутрішнім процесом і не використовуються в традиційних процесах, тому їх називають процесами середньої стадії.

Зазвичай процес підготовки контактного отвору є лінією розмежування між початковим процесом і кінцевим процесом.

Контактний отвір: отвір, витравлений вертикально в кремнієвій пластині для з’єднання лінії з’єднання металу першого шару та пристрою підкладки. Він наповнений таким металом, як вольфрам, і використовується для підведення електрода пристрою до шару з’єднання металу.

Наскрізний отвір: Це шлях з’єднання між двома суміжними шарами металевих з’єднувальних ліній, розташованих у діелектричному шарі між двома металевими шарами, і зазвичай заповнений металами, такими як мідь.

У широкому сенсі:

Інтерфейсний процес: У широкому розумінні, виробництво інтегральних схем має також включати тестування, пакування та інші етапи. Порівняно з тестуванням і упаковкою, виробництво компонентів і з’єднань є першою частиною виробництва інтегральних схем, які разом називаються зовнішніми процесами;

Внутрішній процес: тестування та упаковка називаються внутрішніми процесами.

3. Додаток

SMIF: стандартний механічний інтерфейс

AMHS: автоматизована система передачі матеріалів

OHT: Передача підйомним механізмом

FOUP: уніфікований модуль із переднім відкриттям,Ексклюзивно для пластин розміром 12 дюймів(300 мм)

Що важливіше,Semicera може забезпечитиграфітові деталі, м'який/жорсткий фетр,деталі з карбіду кремнію, CVD деталі з карбіду кремнію, іДеталі з покриттям SiC/TaCз повним напівпровідниковим процесом за 30 днів.Ми щиро сподіваємось стати вашим довгостроковим партнером у Китаї.

Час публікації: 15 серпня 2024 р